Jinsong Zhang

Email: jinsongzhang[at]ucsb[dot]edu

I am currently pursuing a M.S. degree in Computer Engineering at the University of California, Santa Barbara. I previously earned my B.Eng. in Electronic Engineering from the University of Liverpool.

My current research, supervised by Prof. Zheng Zhang, focuses on low-precision tensorized DNN training and hardware acceleration. Previously, I worked in the WINDY Lab under Prof. Shiyu Zhao on autonomous systems.

Outside of academics, I am passionate about envisioning the future of computing architectures, from brain-inspired computing to potential bio-integrations. I also enjoy playing basketball and exploring new landscapes. For my recent work and reflections, you can find them here: Reflections.

News

- [Nov 2025] Our work has been submitted to 2026 63nd ACM/IEEE Design Automation Conference (DAC).

Education

-

University of California, Santa Barbara Sep 2024 - PresentM.S. in Computer Engineering | GPA: 3.78/4.0

-

University of Liverpool Sep 2022 - Jun 2024B.Eng. in Electrical and Electronic Engineering | GPA: 3.7/4.0

-

Xi'an Jiaotong-Liverpool University Sep 2020 - Jun 2022B.Eng. in Electronic Science and Technology | GPA: 3.3/4.0

Skills

- Frameworks & Tools: PyTorch, OpenCV, ROS (Robot Operating System), Git, Linux.

- Programming: C/C++, Python, Verilog, MATLAB, Assembly.

- Hardware Design: Vivado, Vitis, Quartus, Cadence.

Experience

- Teaching Assistant Certification, University of California, Santa Barbara.

- Visiting Student, WINDY Lab, Westlake University (Advisor: Prof. Shiyu Zhao).

- Summer Undergraduate Research Fellowship, Xi'an Jiaotong-Liverpool University.

Selected Research Projects

Submitted to 2026 Design Automation Conference (DAC)

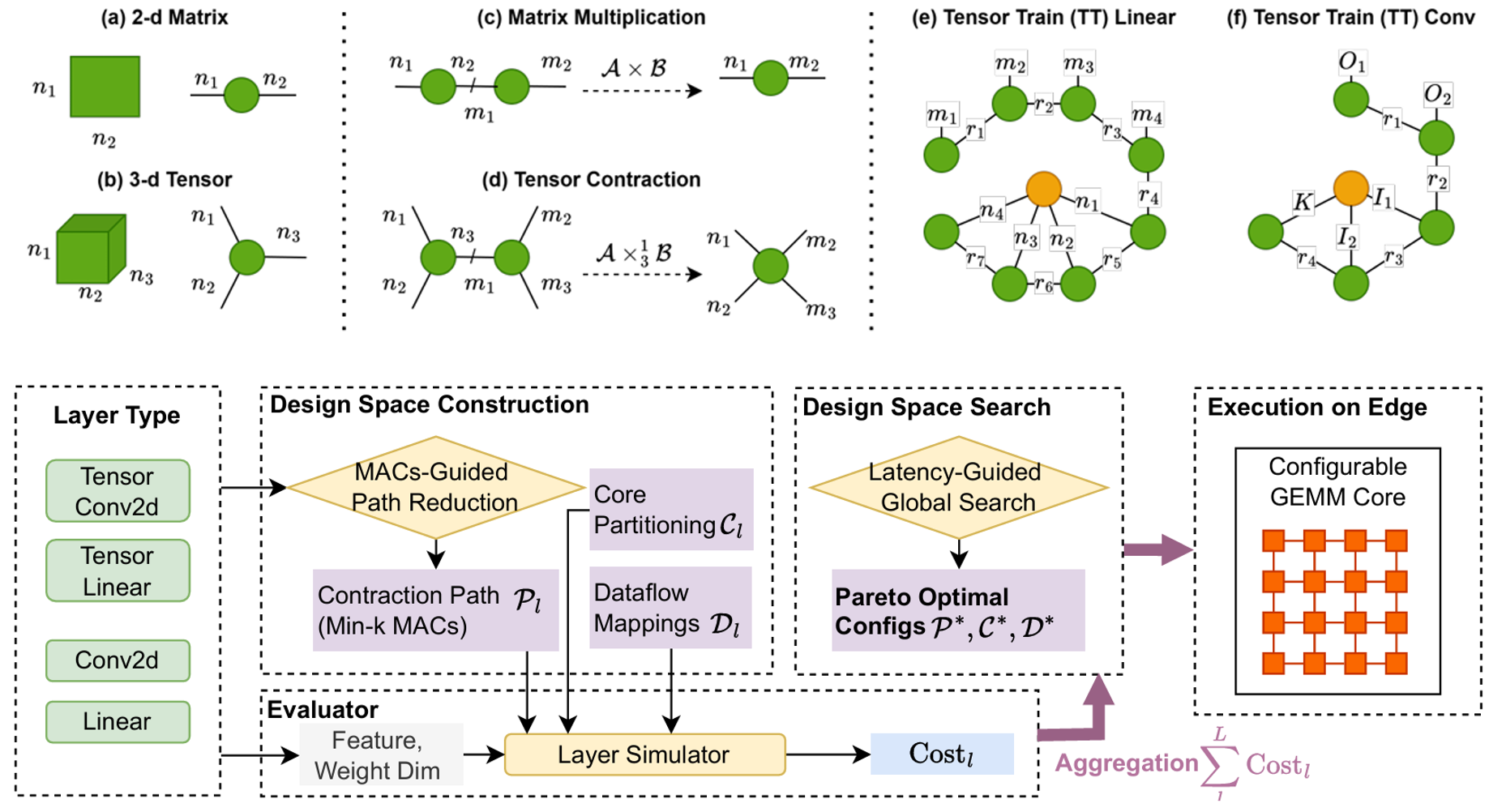

Proposed a novel hardware accelerator architecture for low-precision tensorized neural networks. We performed a comprehensive design space exploration on FPGA, achieving significant improvements in latency and energy efficiency compared to baseline implementations.

Deployed a YOLOv5s object detection model on an embedded platform using the NVIDIA Triton Inference Server. Integrated the perception pipeline with ROS for real-time autonomous navigation of small-scale vehicles.

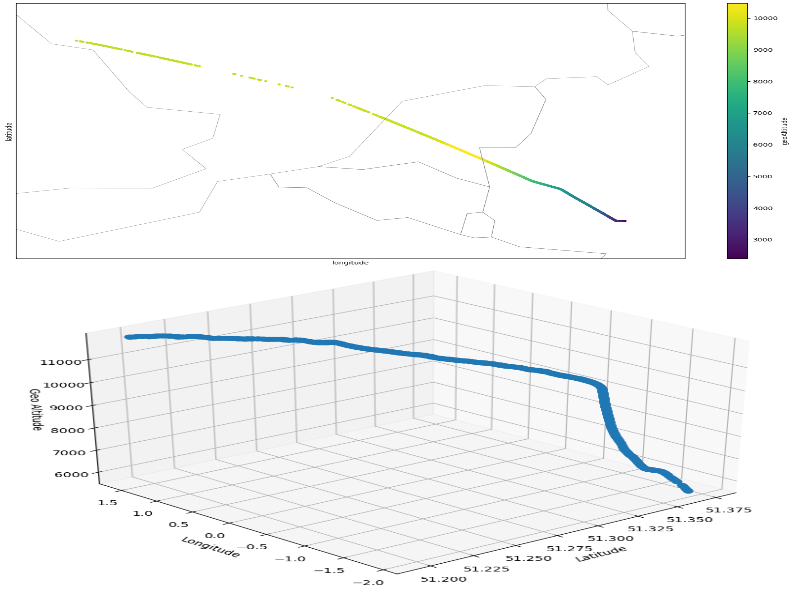

Developed and compared Recurrent Neural Network models (LSTM and GRU) to predict aircraft flight trajectories based on historical ADS-B data. Analyzed prediction accuracy and latency trade-offs.

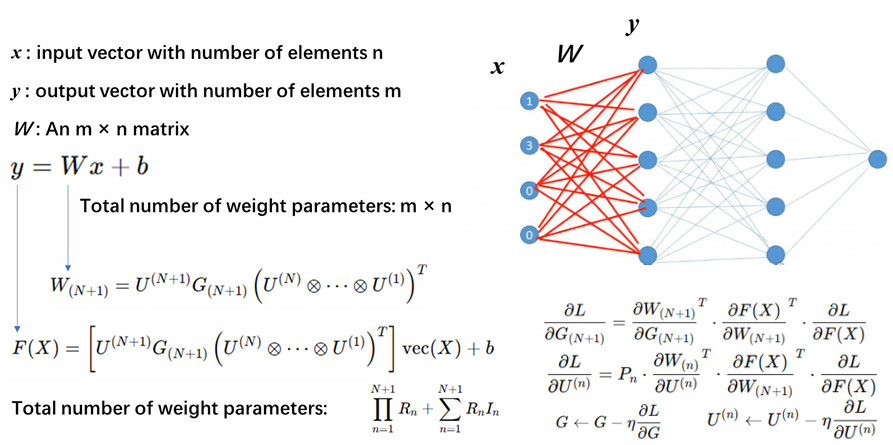

Implemented Tucker decomposition for fully connected layers to reduce model parameter size while maintaining accuracy.

Selected Engineering Projects

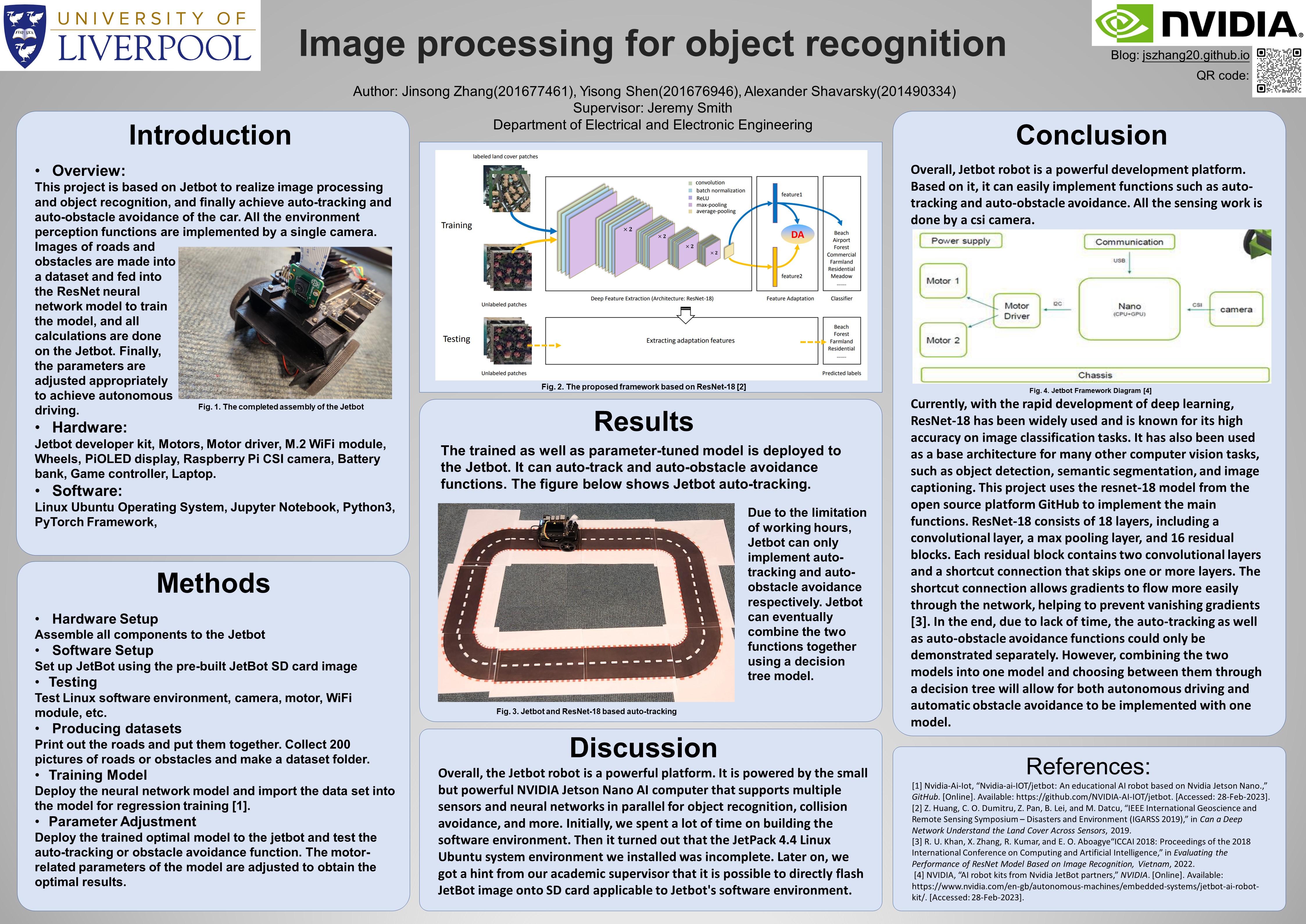

Combined deep learning based perception with classical PID control for lane keeping and navigation.

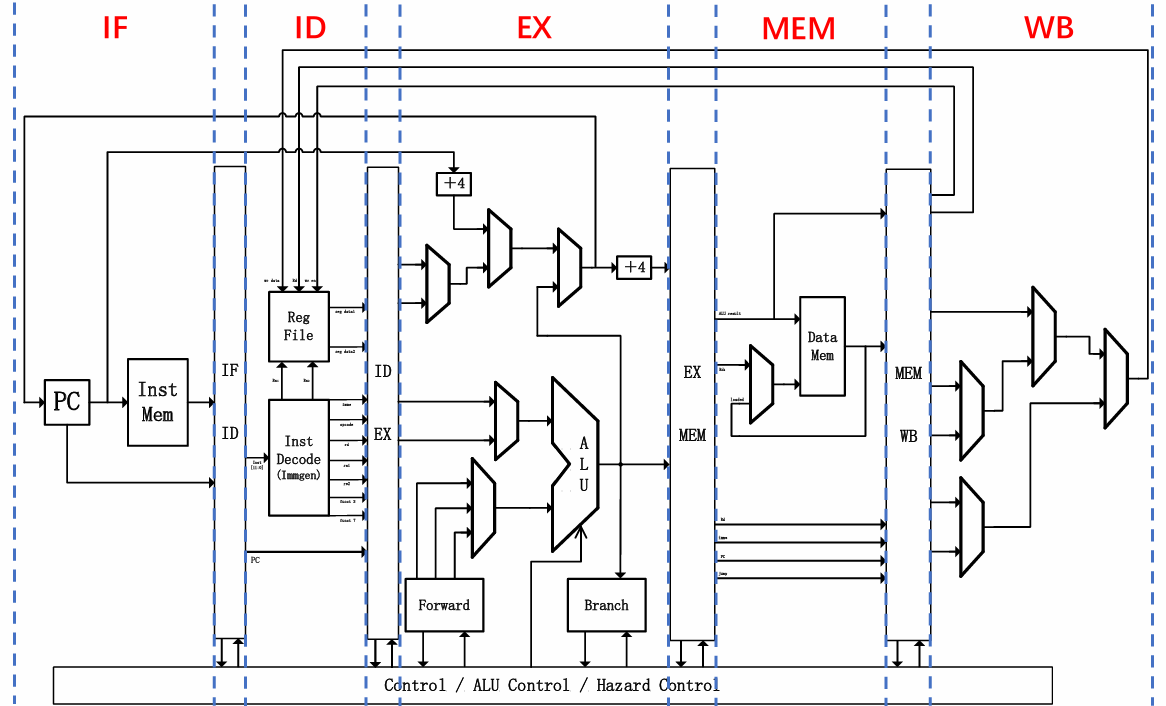

Designed a fully functional 5-stage pipeline processor supporting RV32I instruction set, handling hazards and forwarding.

Integrated laser sensors and IMU data to estimate terrain slope for UAV landing maneuvers.

Implemented a MIPS processor on FPGA using Verilog, extending instruction support.